# AIR BRIDGE BASED PLANAR HYBRID TECHNOLOGY FOR MICROWAVE AND MILLIMETERWAVE APPLICATIONS

E. Wasige, G. Kompa, F. vanRaay, I.W. Rangelow\*, W. Scholz\*; F. Shi\*, R. Kassing\*, R. Meyer\*\*

and M.-C. Amann\*\*

FG Hochfrequenztechnik/AGTechnischePhysik\*/TechnischeElektronik\*\*

University of Kassel

D-34121 Kassel, Wilhelmshöher Allee 73

Tel: +49-561-804 6364, Fax: +49-561-804 6529

E-mail: wasige@hfm.e-technik.uni-kassel.de

## ABSTRACT

A new silicon based, planar hybrid technology is being developed to address limitations associated with packaging and interconnections. The approach combines the advantages of both hybrid and monolithic technologies. Microwave transistor chips (GaAs FETs) are integrated in high resistivity silicon substrates with a vertical precision of better than 2  $\mu\text{m}$  and lateral tolerances less than 10  $\mu\text{m}$ . Air bridge technology and thin film techniques are then used to provide the necessary interconnections. The basic features of the proposed technology are presented here.

## INTRODUCTION

Packaging and interconnections are increasingly becoming the limiting factors in system performance. The availability of low-cost and reproducible microwave and millimeterwave circuits is of great importance to systems in the future. A promising way to meet these requirements are integrated circuits based on silicon substrate [2], [10], [13]. Microwave devices such as FETs which are suitable for applications in this frequency range are, however, based on GaAs because of its superior electrical performance. Consequently, GaAs based device technologies, e.g. for MESFETs and HEMTs, are well developed.

Commercial HEMT chips covering frequencies beyond 60 GHz are available [9]. Generally, hybrid technologies have therefore been used for many different applications as a good compromise between cost and performance e.g. [1], [3].

In the classical hybrid integration approach, active devices are mounted on top of the substrate and the interconnections are made by bonding wires. Such interconnections are not reproducible and at microwave frequencies exhibit undesirable parasitic inductances which degrade and limit the circuit performance and bandwidth respectively. A technology that circumvents these limitations is Flip Chip bonding [1], [8], [14]. Devices are manufactured with suitable bonding pads leading to very short and reproducible interconnections. However, a large number of microwave devices, either low-noise or low-power do not have bump contacts and must be bonded [3]. Planar interconnect technologies focusing specifically on low-power microwave devices have been reported [5], [6]. The proposed technologies also require very short interconnections which, however, must be carried out in a bonding step.

This paper presents a novel hybrid technology whereby GaAs FET devices are integrated in a silicon substrate in a planar position and interconnections made by employing air bridge technology as in monolithic circuits. The approach takes advantage of the conventional silicon micromachining technology, thin film technology

and, as active devices, commercially available GaAs FETs in chip form. The high resistivity silicon substrate serves as a basis for realizing distributed passive coplanar components.

## THE NEW TECHNOLOGY APPROACH

The proposed technology is based on two main steps, namely planar integration of the GaAs FETs in Si substrate and thin film/air bridge interconnections of the embedded chip to the rest of the circuit.

### a) Planar Embedding Technique

This is the first and most important technological step. The aim here is to make an opening in a substrate and then glue an active device in it such that a plane surface between the active device and substrate results. This must be attained to guarantee for the successful subsequent processing associated with lithography and metallisation.

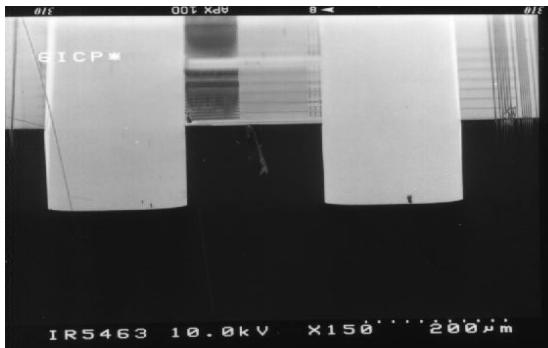

Two possibilities, wet etching or dry etching, exist for micromachining of silicon. Dry etching with inductively coupled plasma and cryo-temperature of the substrate allows the etching of grooves with vertical sidewalls and etching rates up to 2 to 4  $\mu\text{m}/\text{min}$  (Fig. 1) [12]. Although the cross-sectional dimensions of an opening for a chip can be exactly defined, the etching depth is difficult to control without laser interferometry. Wet etching of silicon (with  $<100>$  crystal orientation) results in slanting sidewalls. The resulting gap between a mounted chip and silicon is impossible to planarize [15]. A technique based on wet etching of openings in Si and using a planarization adhesive film was therefore developed.

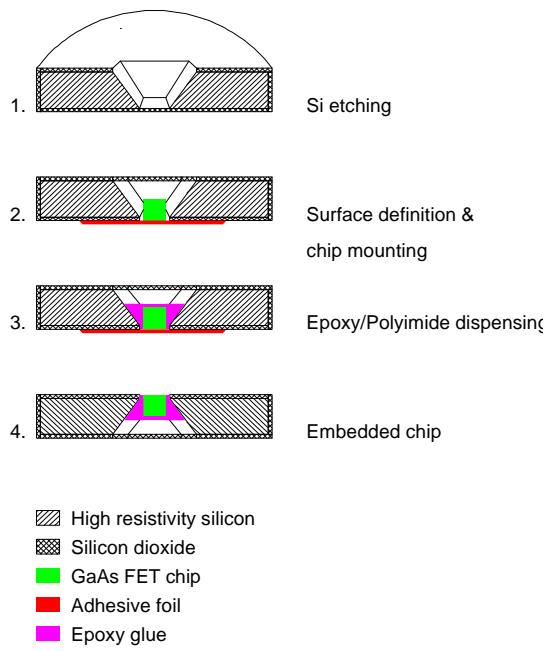

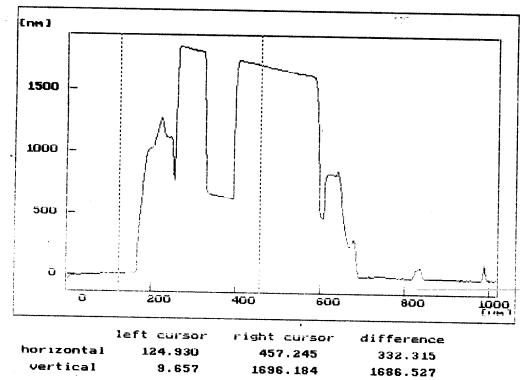

Fig. 2 shows a summary of the procedure developed for high precision mounting of chips in a substrate. A silicon substrate is etched in KOH solution at the required opening positions. Next, an adhesive film is spanned with care to cover the opening. A chip is then introduced face down into the substrate and positioned on the adhesive film. The gaps between the chip and the substrate are filled out with an epoxy resin (Epo-Tek H77-S) or polyimide. After the glue dries up, the adhesive film is pulled away leaving a plane surface. A surface planarity of less

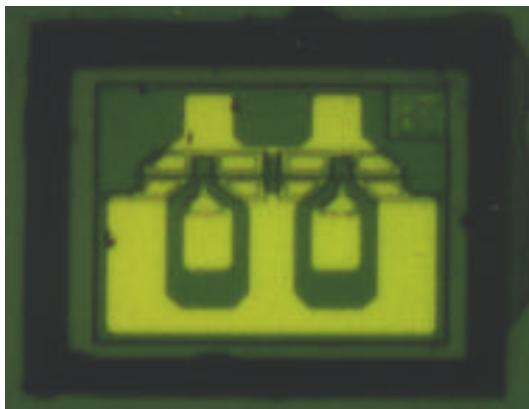

than 2  $\mu\text{m}$  has been achieved. A scan of the surface profile across an embedded chip and the surrounding substrate area is shown in fig. 3. A typical low-noise microwave transistor chip has dimensions of the order 350x400x100  $\mu\text{m}$  which calls for very fine handling. Although similar techniques have been proposed for multi chip modules in general [4], [7], [11], they have not yet been investigated for microwave applications.

### b) Interconnection Technology

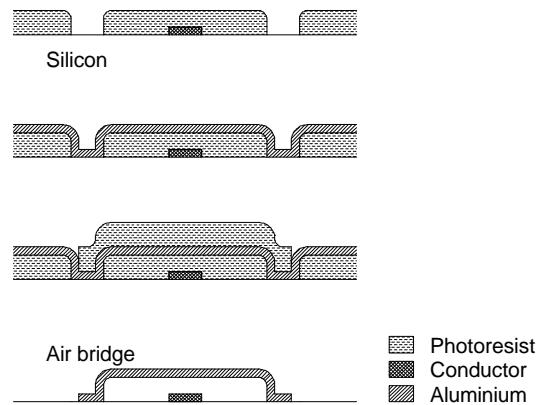

The interconnections to the embedded active device are realized by using air bridge technology. This technology offers low parasitic interconnect capacitance and low inductance. Furthermore, this technique eliminates uncertainty that may be caused by the small non-planarity of the surface. A cheaper technology based on aluminium rather than standard gold plated bridges has been developed. Fig. 4 depicts a schematic diagram of this air bridge fabrication technique. The use of aluminium though not mandatory allows a further option to re-use accurately characterized low-power devices in final circuit fabrication. If the basic circuit is to be fabricated using gold metallization, the aluminium air-bridge interconnections on the micro-test-fixture [15] can be selectively etched away allowing the final circuit and new interconnections to be fabricated.

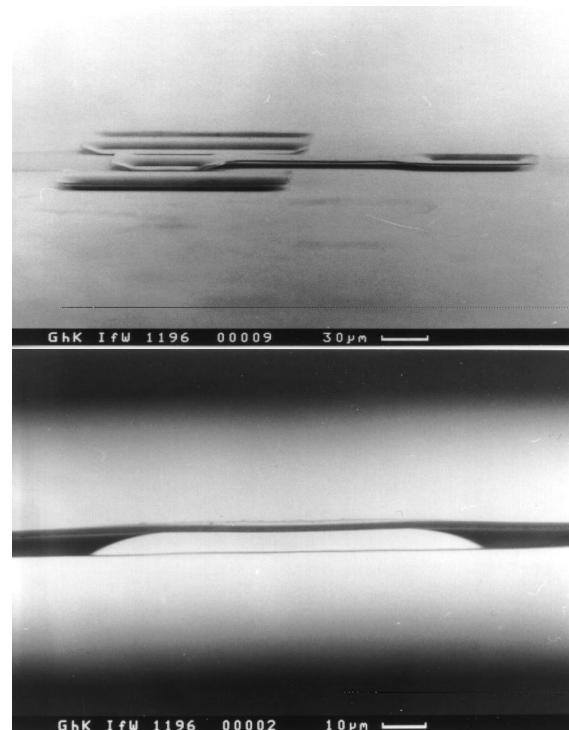

First a thick layer of photoresist is spun on the substrate and patterned. After a careful bake of the resist for removing all solvents a 2  $\mu\text{m}$  thick aluminium layer is evaporated under rotating/swaying motion of the substrate for uniform covering of the resist slopes/edges. Then a second layer of photoresist is spun on and patterned. The extra aluminium is etched away and finally the resist is stripped leaving stable air bridges. Fig. 5 shows scanning electron micrographs of test air bridges. The aluminium thickness is 2  $\mu\text{m}$  and the headroom width is 6  $\mu\text{m}$ .

A silicon micro-test-fixture based on a preliminary version of this technology using bondwires instead of air-bridges was presented elsewhere [15]. A number of low-power microwave circuits are still under investigation and a comprehensive analysis of the results will be presented at a later date.

## CONCLUSIONS

A low-cost hybrid technology for microwave circuits has been described. GaAs FET devices have been integrated in a quasi-monolithic manner in silicon substrates. Planar, very short and reproducible interconnections complete the simple assembly with promising microwave performances at low-cost.

## ACKNOWLEDGEMENTS

The authors would like to thank S. Bertram and H. Hohmann for the fabrication of the air-bridges and Dr. Peter Hudek (Slovak Academy of Sciences) for providing several masks required for the project. The financial support received from the University of Kassel is gratefully acknowledged.

## REFERENCES

- [1] Baumann G., Ferling D., and Richter H.: Comparison of flip chip and wire bond interconnections and the technology evaluation on 51 GHz transceiver modules, 26th *European Microwave Conference*, Sept. 1996, pp. 98-100.

- [2] Beisswanger F. et al: Microstrip and coplanar SiGe-MMIC oscillators, 26th *European Microwave Conference*, Sept. 1996, pp 588-592.

- [3] Belohoubek E.: Miniature Microwave Circuits - Alternative to Monolithic Circuits, *RCA Review* 46, Dec. 1985, pp. 464-483.

- [4] Buschick K. et al: Multichipmodule auf der Basis von Einbettechniken, *VDI Berichte Nr. 960*, 1992, pp. 497-508.

- [5] Fathy A., Brown R., Belohoubek E.: Miniature gain Block for Satellite Communication Receivers, *IEEE MTT-S Digest* 1987, pp 565-567.

- [6] Güngerich V., Schadel R., Ramisch R., and Russer P.: A Process for Inserting Chips into Planar Microwave Structures on Semiconductor Substrates, *Microelectronic Engineering* 18 (1992) pp. 247-252.

- [7] Johnson R. W. et al.: Planar hybrid interconnection technology, *International Journal of Hybrid Microelectronics*, vol 10, no. 1, 1987, pp. 28-35.

- [8] Krems T., Haydl W., Massler H., and Rüdiger J.: Millimeter-Wave Performance of Chip Interconnections Using Wire Bonding and Flip Chip, *IEEE MTT-S Digest* 1996, pp. 247 - 250.

- [9] Lunden O.-P., Sipilä M., and Jenu M.: A 60 GHz LNA using commercially available PM HEMTs for intersatellite and mobile communications, *IEEE MTT-S Digest*, 1994, pp. 1341-1344.

- [10] Luy J.-F. and Russer P. (Eds.): *Silicon-Based Millimeter-Wave Devices*, Berlin: Springer, 1992.

- [11] Müller H.G. et al.: Plane surface embedding technique for thin film hybrids, *Proc. 1st Conf. on Microsystems* pp. 335-340, Berlin, 1990.

- [12] Rangelow I. W. and Löschner H.: Reactive ion etching for microelectrical mechanical system fabrication, *J. Vac. Sci. Technol. B* 13(6), Nov/Dec 1995, pp.2394-2399.

- [13] Reyes A. C., El-Ghazaly S.M. et al.: Coplanar Waveguides and Microwave Inductors on Silicon Substrates, *IEEE Trans. on Microwave Theory and Techniques*, MTT-43, No. 9, September 1995, pp. 2016-2022.

- [14] Sturdivant R.: On The Performance of GaAs MMIC Flip Chips, *IEEE MTT-S Digest*, pp 1591-1594, 1994.

- [15] Wasige E., Kompa G., van Raay F., Rangelow I.W., Shi F., Scholz W., and Kassing R.: A New Silicon Micro-test-fixture Facilitates the Re-usability of Accurately Characterized Low-Power FET Devices, 26th *European Microwave Conf.*, Sept. 1996, pp. 521-523.

Fig. 1: Cross-section of grooves etched with  $\text{SF}_6/\text{O}_2$  plasma at a substrate temperature of  $-100^\circ\text{C}$ .

Fig. 2: Procedure for high precision integration of GaAs FETs in Si substrate.

Fig. 3: (a) Top view of GaAs PHEMT chip mounted in a Si Substrate.

Fig. 3: (b) Profilometer scan of the chip in (a)

Fig.4: Fabrication steps for the air bridges.

Fig. 5: Scanning Electron Micrographs (SEM) of test air bridges.